El procedimiento es mucho más sencillo que con ModelSIM. Hay que asegurarse de haber seleccionado ISim como simulador a la hora de crear el proyecto.

Para poder estimular a la Arduino se necesitan, por lo menos, dos cosas: un reloj y una señal de reset. Esto se hace desde un banco de trabajo o testbench. En el código de Gadget Factory se facilita uno, en scripts\XilinxISE\testbench.vhd. En el menú Project se selecciona "Add copy of source" y se busca este fichero.

Antes de simular se deben hacer algunos cambios, abriendo el testbench con doble click:

Cambiar

constant clk_period : time := 1us;

por

constant clk_period : time := 31.25 ns;

Para que el reloj sea de 32Mhz.

Además hay que comentar estas dos líneas:

portb <= "11111111";

portd <= "10101010";

Que deben quedar de esta forma:

--portb <= "11111111";

--portd <= "10101010";

El programa de Arduino que vamos a grabar para la prueba es el siguiente:

int ledPin = 13; void setup() {

pinMode(ledPin, OUTPUT);

}

void loop() {

digitalWrite(ledPin, HIGH); // set the LED on

digitalWrite(ledPin, LOW); // set the LED off

}

Que simplemente hace parpadear el pin 13 constantemente.

En la ventana Files de ISE se edita prog_mem_init.vhd y se reemplazan las siguientes líneas:

constant PM_Inst_RAM_Word0_INIT_00 : bit_vector(0 to 255) := x"00B1940C00B1940C00B1940C00B1940C00B1940C00B1940C00B1940C008E940C"; constant PM_Inst_RAM_Word0_INIT_01 : bit_vector(0 to 255) := x"00B1940C00B1940C00B1940C00B1940C00B1940C00B1940C00B1940C00B1940C"; constant PM_Inst_RAM_Word0_INIT_02 : bit_vector(0 to 255) := x"00B1940C00B1940C00B1940C00B1940C00B1940C00B1940C00B1940C013B940C"; constant PM_Inst_RAM_Word0_INIT_03 : bit_vector(0 to 255) := x"0039000000270023003200350038003B000000280022003100340037003A0000"; constant PM_Inst_RAM_Word0_INIT_04 : bit_vector(0 to 255) := x"0303030303030202020202020202010101010101010100200021003000330036"; constant PM_Inst_RAM_Word0_INIT_05 : bit_vector(0 to 255) := x"2010080402010606060606060606050505050505050504040404040404040303"; constant PM_Inst_RAM_Word0_INIT_06 : bit_vector(0 to 255) := x"2010080402018040201008040201804020100804020180402010080402018040"; constant PM_Inst_RAM_Word0_INIT_07 : bit_vector(0 to 255) := x"0000000000000500000100000000000000000000000080402010080402018040"; constant PM_Inst_RAM_Word0_INIT_08 : bit_vector(0 to 255) := x"BE1F241100000000000000000000000000000000000000000000000000000000"; constant PM_Inst_RAM_Word0_INIT_09 : bit_vector(0 to 255) := x"9631920D95D8C004BF0B9503EF0FE0F3E3E8E0B0E6A0E010BFCDBFDEE0DFEFCF"; constant PM_Inst_RAM_Word0_INIT_0A : bit_vector(0 to 255) := x"940C0134940EF7E107B136AB921DC001E0B0E6A2E010BE1BF7C907B136A2F3C8"; constant PM_Inst_RAM_Word0_INIT_0B : bit_vector(0 to 255) := x"00609180950800EC940EE0600060918000EC940EE061006091800000940C019A"; constant PM_Inst_RAM_Word0_INIT_0C : bit_vector(0 to 255) := x"4F3F57262D9095C82FF92FE84F9F54862F932F82E0302F28950800C4940EE061"; constant PM_Inst_RAM_Word0_INIT_0D : bit_vector(0 to 255) := x"95C896312DA095C84FFF5AE01FFF0FEEE0F02FE8F0A923882D8095C82FF32FE2"; constant PM_Inst_RAM_Word0_INIT_0E : bit_vector(0 to 255) := x"2F952F84E0502F489508938C2B89918C9508938C23899590918CF42923662DB0"; constant PM_Inst_RAM_Word0_INIT_0F : bit_vector(0 to 255) := x"4F5F57462D9095C82FF92FE84F9F54862F952F842D2095C82FF92FE84F9F5186"; constant PM_Inst_RAM_Word0_INIT_10 : bit_vector(0 to 255) := x"B58FF4213024C004778FB58FF4193023F0B12322F16923332D3095C82FF52FE4"; constant PM_Inst_RAM_Word0_INIT_11 : bit_vector(0 to 255) := x"E0F02FE3BD857D8FB585F4193025C005BF837D8FB783F4213021C00BBD8F7D8F"; constant PM_Inst_RAM_Word0_INIT_12 : bit_vector(0 to 255) := x"9508938C23899590918CF42923662DB095C896312DA095C84FFF59E21FFF0FEE"; constant PM_Inst_RAM_Word0_INIT_13 : bit_vector(0 to 255) := x"2411920FB60F920F921FCFFD00B3940E00BE940E0183940E9508938C2B89918C"; constant PM_Inst_RAM_Word0_INIT_14 : bit_vector(0 to 255) := x"006A9130006991B0006891A0006791900066918093BF93AF939F938F933F932F"; constant PM_Inst_RAM_Word0_INIT_15 : bit_vector(0 to 255) := x"939000669380006A93201DB11DA19601572DF020372D5F2D2F231DB11DA19601"; constant PM_Inst_RAM_Word0_INIT_16 : bit_vector(0 to 255) := x"1DB11DA19601006591B0006491A00063919000629180006993B0006893A00067"; constant PM_Inst_RAM_Word0_INIT_17 : bit_vector(0 to 255) := x"BE0F900F912F913F918F919F91AF91BF006593B0006493A00063939000629380"; constant PM_Inst_RAM_Word0_INIT_18 : bit_vector(0 to 255) := x"BD8E6081B58EBD8E6082B58EBF876081B787BF836084B78394789518901F900F"; constant PM_Inst_RAM_Word0_INIT_19 : bit_vector(0 to 255) := x"000000000000000DCFFF94F89508BD856081B585BD856082B585BD8F6081B58F"; constant PM_Inst_RAM_Word0_INIT_1A : bit_vector(0 to 255) := x"0000000000000000000000000000000000000000000000000000000000000000"; constant PM_Inst_RAM_Word0_INIT_1B : bit_vector(0 to 255) := x"0000000000000000000000000000000000000000000000000000000000000000";

El programa sólo ocupa estas líneas, desde INIT_00 hasta INIT_19. El resto de líneas se rellenan con ceros. La explicación de compilar programas Arduino y convertirlos en este formato se hará más adelante.

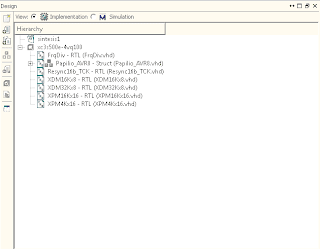

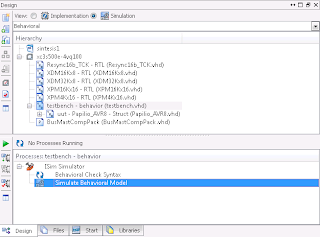

Una vez guardado el fichero, se vuelve a la ventana Design y se selecciona la vista Simulation. Al seleccionar testbench, se habilita el proceso Simulate Behavioral Model. Al hacer doble click sobre él se abre ISim.

En la barra de herramientas

se escribe 300us y se pincha en el tercer icono, "Run for the time specified on the toolbar".

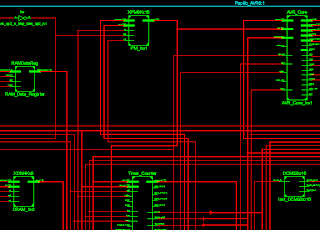

En el visor de señales se comprueba perfectamente que el pin 13 (pin 5 del puerto B) parpadea tal y como estaba previsto.

Se puede comprobar que digitalWrite es una función muy lenta ya que tarda 15 microsegundos en cambiar de estado.

Parte V - Compilar programas Arduino para simulación

Índice del tutorial